MYD-C7Z015 Development Board - MYD-C7Z015

Click to enlarge |

|

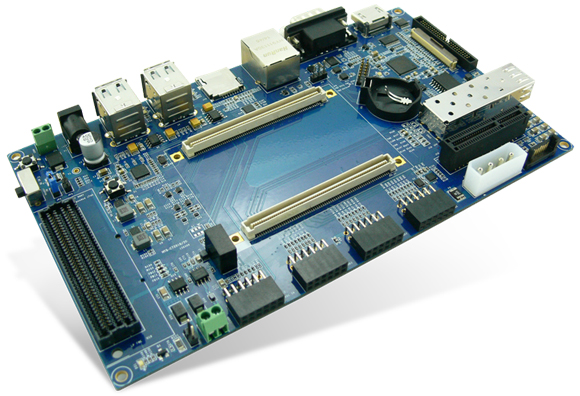

MYD-C7Z015 Development Board |

|

|

Description

The MYD-C7Z015 development board is a programmable, low-cost and high-performance board designed by MYIR. It integrates Xilinx XC7Z015 (Z-7015) Dual-core ARM Cortex-A9 Processor with Xilinx 7-series FPGA logic from Xilinx Zynq-7000 family, with one PCIe interface and one SFP transceiver module interface on the base board to allow users to expand numerous of high-speed devices. It’s typically applications ranges from Industrial Automation, Test & measurement, Medical Equipment, Aerospace to military and more others.

The MYD-C7Z015 development board is using the MYC-C7Z015 CPU Module as the core controller board which integrates the core components including the Zynq-7015 processor, 1GB DDR3 SDRAM, 4GB eMMC, 32MB quad SPI Flash, a Gigabit Ethernet PHY, a USB PHY and external watchdog. The MYC-C7Z015 CPU Module is mounted on to the MYD-C7Z015 base board through two 0.8mm pitch 140-pin Board-to-Board connectors. Compared with the Zynq-7010, the processor Zynq-7015, has more logic cells, Block RAM and DSP slices, which makes the board obtain more powerful programmable function for users.

The MYD-C7Z015 development board is using the same base board with MYD-C7Z010/20 development board and takes full features of the Zynq-7015 SoC to create a rich set of peripherals to the base board through headers and connectors including one RS232 serial port, four USB Host ports, one Gigabit Ethernet port, CAN, HDMI, LCD/Touch screen, TF card slot, RTC, one XADC header to allow you take advantage of Xilinx XADC, three PMoD headers to meet your I/O needs with PMoDs and one low-pin count FMC connector to allow various FMC cards for custom I/O options. Especially, it has one SFP transceiver module to keep higher transmission speed and better stability during your evaluation, as well as one PCIe interface, which contributes the data transmission speed to a high frequency when customers using the board.

The MYD-C7Z015 development board is preloaded with Linux and delivered with necessary cable accessories. It is a high-performance and low-cost development platform for evaluation and prototype based on Xilinx Zynq-7000 All Programmable SoC family.

MYD-C7Z015 Development Board

Features

Mechanical Parameters

- Dimensions: 190mm x 110mm (base board), 75mm x 55mm (CPU Module)

- PCB layers: 4-layer design (base board), 12-layer design (CPU Module)

- Power supply: 12V/0.5A (base board), 5V/0.5A (CPU Module)

- Working temp.: 0~70 Celsius (commercial grade)

OS Support

- Linux 3.15.0

The MYD-C7Z015 Controller Board (MYC-C7Z015 CPU Module)

SoC

-

Xilinx XC7Z015-1CLG485C (Zynq-7015)

- 667MHz ARM® dual-core Cortex™-A9 MPCore processor (up to 866MHz)

- Integrated Artix-7 class FPGA subsystem with 74K logic cells, 46,200 LUTs, 160 DSP slices (for XC7Z015)

- NEON™ & Single / Double Precision Floating Point for each processor

- Supports a Variety of Static and Dynamic Memory Interfaces

- Four high-speed SerDes transceivers up to 6.25Gbps

- Four PCIe Gen2 hardened, integrated IP blocks

Memory

- 1GB DDR3

- 4GB eMMC

- 32MB QSPI Flash (16MB is optional)

Peripherals and Signals Routed to Pins ( MYC-C7Z015 pin-out description)

MYC-C7Z015 pin-out description)

- One 10/100/1000M Ethernet PHY with SGMII

- One USB 2.0 ULPI PHY

- External watchdog

-

Three LEDs

- One blue LED for power indicator

- One red LED for FPGA program done indicator

- One green user LED -

Two 0.8mm pitch 140-pin board-to-board expansion connectors bring out below signals:

- One Gigabit Ethernet (PS Ethernet 0)

- One USB OTG 2.0 (PS USB 0)

- Two Serial ports (reused from PS_MIO, can also be implemented through PL pins)

- Two I2C (reused from PS_MIO, can also be implemented through PL pins)

- Two CAN BUS (reused from PS_MIO, can also be implemented through PL pins)

- One SPI (reused from PS_MIO, can also be implemented through PL pins)

- ADC (one independent differential ADC, 16-channel ADC brought out through PL pins)

- One SDIO (PS SDIO 0)

- Bank 13 (PL I/O configurable as up to 18 LVDS pairs and 1 single-ended I/O or 37 single-ended I/O)

- Bank 34 (PL I/O configurable as up to 24 LVDS pairs and 2 single-ended I/O or 50 single-ended I/O)

- Bank 35 (PL I/O configurable as up to 24 LVDS pairs and 2 single-ended I/O or 50 single-ended I/O)

- Bank 112 (4 GTP serial transceivers, 2 reference clock input)

The MYD-C7Z015 Base Board (MYB-C7Z015)

MYD-C7Z015 Base Board (MYB-C7Z015)

PS Unit

- Four USB 2.0 Host ports (through USB Hub)

- One RS232 (DB9 port)

- One TF card slot (bootable)

- One CAN interface

- One 10/100/1000M Ethernet

- One 2.54mm pitch 14-pin JTAG interface (PS, PL reused)

- Battery backed RTC

- One User Button (One I2C, can be connected to LCD and Resistive Touch Screen)

- Jumpers - One for booting selection from TF card or QSPI- One for JTAG selection for using PS and PL reused or independent JTAG configured through PL pins- One for selection if adding FMC module to JTAG

PL Unit

- One XADC interface

- One Xilinx standard LPFMC interface

- One HDMI interface (16-bit YCrCb, support 1080p display, do not support audio)

- LCD/Touch screen interface (16-bit RGB, signals reused with HDMI, supports resistive and capacitive touch screen)

- Two LEDs (one for FMC module detection, one for power indicator)

- Three-channel PMoD

- One SFP transceiver module with RJ45 interface(SFP-GE-T module, up to 1000Mbps)

- One PCIe interface

Your Review: Note: HTML is not translated!

Rating: Bad Good

Enter the code in the box below:

Categories

Categories Brands

Brands Information

Information Shopping Cart

Shopping Cart Bestsellers

Bestsellers